在验证嵌入式系统中的电源完整性时,有两个主要考虑因素;各种电源转换器的运行和配电系统的完整性。这两个考虑因素的相对重要性部分取决于所使用的电力系统架构。在具有集中式多输出 ac/dc 电源的系统中,电源认证相对更为重要。本系列之前的常见问题解答集中在“如何验证交流/直流电源性能”。本常见问题解答将关注影响配电系统完整性的因素,尤其是在使用分布式电源架构 (DPA) 的系统中。

DPA 中使用相对高压的配电总线向各个子系统供电。配电总线电压的范围可以从 12Vdc 到 720Vdc 甚至更高,具体取决于系统的大小和功能。DPA 多年来一直用于计算机服务器、电信和其他嵌入式设备。最近,DPA 已在运输和机器人系统中得到应用。

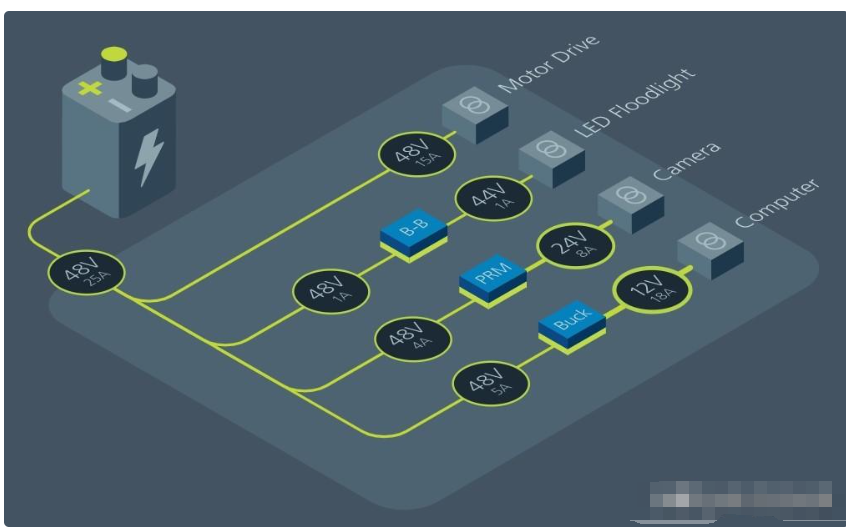

分布式电源架构用于越来越多的应用,从计算机系统到运输和机器人技术。(图片:维克)

上图显示了可用于汽车或机器人应用的中型 DPA。48Vdc主电源总线可直接为汽车中的泵和风扇或机器人中的动力等各种功能的电机供电。48Vdc 配电电压可下变频为 24Vdc 至 44Vdc 之间的电压,以驱动各种 LED 照明、相机、LIDAR 等。它可以转换为 12Vdc,为中间配电总线供电,用于各种数字和模拟功能,并使用附加的非隔离负载点 (PoL) dc/dc 转换器为“计算机”部分中的功能供电。

随着 DPA 电压越来越低,确保电源完整性 (PI) 的挑战变得越来越重要和困难。特别是在上图的计算机部分,ASIC 和 FPGA 等数字 IC 可能需要 1Vdc 或更低的电压和高达 100 安培的电流。在这些层面上,PI 是一个严峻的挑战。

配电网阻抗

在嵌入式系统中,PI 分析是系统设计的一个重要方面,而分析配电网络 (PDN) 阻抗是该分析的关键部分。PI 分析确定所需的电压和电流是否准确地传送到负载。PI 由几个相关元素组成,从芯片开始,到芯片封装,再到电路板 (PCB),最后到系统级。需要优化四个 PDN 性能因素以确保 PCB 上的 PI:

各种芯片电源引脚的电压纹波必须在规格范围内(通常在 1V 左右的 +/-50 mV 变化范围内)

必须控制地反弹。接地反弹有时称为同步开关噪声或同时开关噪声 (SSN),或同时开关输出 (SSO)。

保持电磁兼容性(EMC)和控制电磁干扰(EMI)。配电网络通常是 PCB 上最大的一组导体,可以显着影响 EMC 和 EMI。

控制和最小化各种 PoL 和负载之间的直流电压降。ASIC、FPGA、MCU 和其他大型数字 IC 的电源需求可以在低于 1Vdc 的 VDD 电平下从 1 安培快速摆动到 100+ 安培,电压裕量为数十毫伏。

控制 PDN 中的各种阻抗对于系统正常运行至关重要。动态电流变化是一个特别重要的考虑因素。动态电流变化通常远大于 PoL(在下图中称为 VRM 或稳压器模块)所能提供的,并可能导致降低轨上的电压或导致电压尖峰产生电压纹波. 去耦电容器的尺寸必须适当,以应对不断变化的电流需求。设计人员应仔细检查为各种 PoL 指定的最大输出电容。过多的电容会降低电源转换器的性能。

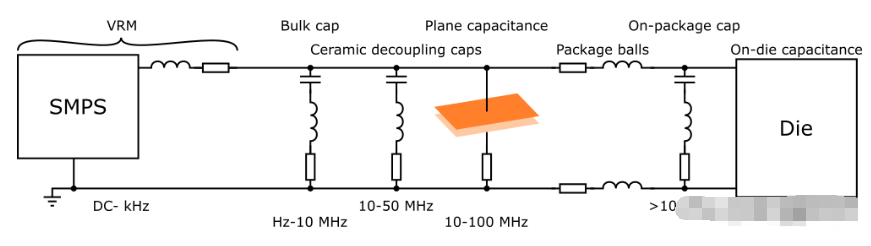

具有运行频率的典型配电网络(图片:维基百科)

如上图所示,电压纹波频域在 PDN 中的不同点发生变化。最高频率通过裸片本身的去耦来处理。高达 100MHz 的中频通常在封装中处理。低于 100MHz 的频率通常留给 PCB 设计人员使用平面电容和去耦电容的组合。

由于 PDN 中不同点的频率范围不同,因此使用了不同类型和大小的电容器。控制(最小化)去耦电容器的寄生电感是一个重要的设计考虑因素。寄生电感会在特定频率产生阻抗尖峰。由于电容器的物理尺寸会影响其寄生电感,因此通常建议设计人员尽可能使用较小的电容器。最小值电容应直接靠近 IC 的引线放置。

每个设计都有一个阻抗目标,在这个目标上,动态电流产生的纹波在要求的范围内。目标阻抗与动态电流的各种频率和预期水平有关。在设计高性能 PDN 时,通常采用仿真来确保达到目标阻抗。根据具体情况,可以使用 SPICE、EDA 软件工具,甚至芯片和/或电容器供应商提供的仿真工具来完成仿真。

噪声和抖动表征

今天的高速数字系统需要低抖动的振荡器和时钟。一个重要的考虑因素是这些振荡器和时钟在系统的非理想 PDN 中的表现。通常需要 100 fs 或更好的抖动性能,指定用于 12kHz 至 20MHz 的集成范围。与可以在设计过程中模拟的目标阻抗不同,需要测量噪声和抖动。虽然理想的 PDN 将提供最佳的噪声和抖动性能,但实际系统性能的测量是必要的。

50Hz 至几 MHz 的频率范围通常用于测量电源线频率和 DC/DC 转换器电源开关频率的电源抖动抑制。测试是通过将给定频率的正弦干扰叠加到直流轨电压上来完成的。相对于电源轨干扰的电压电平(也以 dBm 为单位)的相位噪声线的量(以 dBm 为单位)是干扰频率下的 PSNR。在多个频率上执行测试以在所需频率范围内生成 PSNR 曲线。

电源轨排序

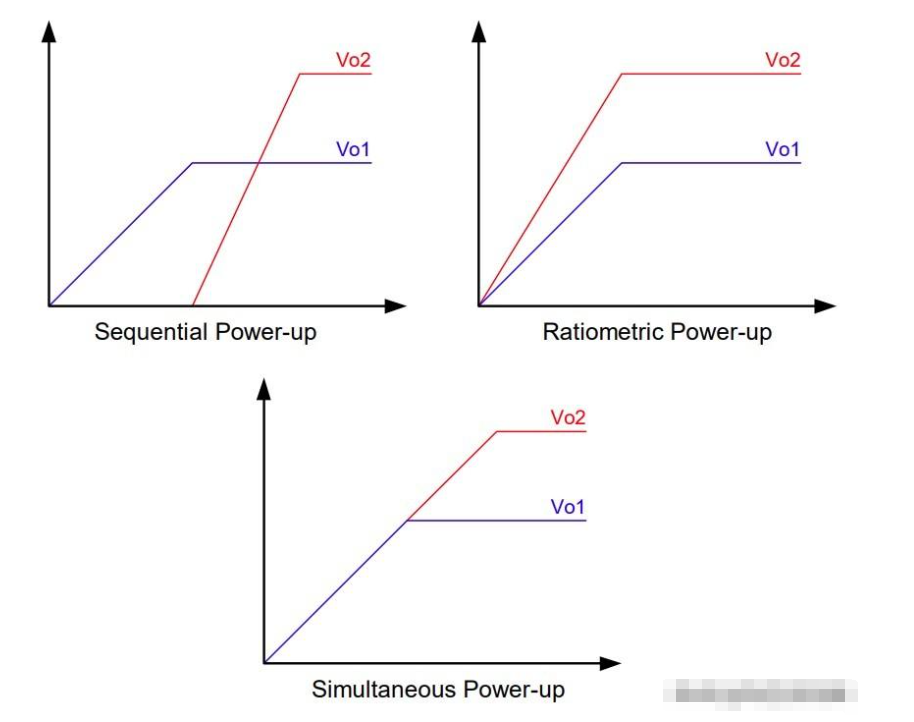

当今的大多数高性能数字 IC 都使用多个严格调节的电压轨。还需要各种电压轨以特定速率和特定顺序上电和断电。违反供电要求会导致 IC 闩锁和/或降低设备的长期可靠性。三种最常见的电源排序实现是顺序、比例和同步:

顺序排序按顺序为每个导轨上电和下电。通常,在下一条铁路启动之前,允许各种铁路达到其运行水平。

比率排序同时为各个轨道供电,每个轨道同时达到规定。为了使差分电压比保持恒定,电压轨越高,压摆率越高。

同步排序同时为轨道通电,并且轨道具有相同的转换速率,从而最大限度地减少各个轨道之间的差分电压。

典型电源排序方法的示例。(图片:英飞凌)

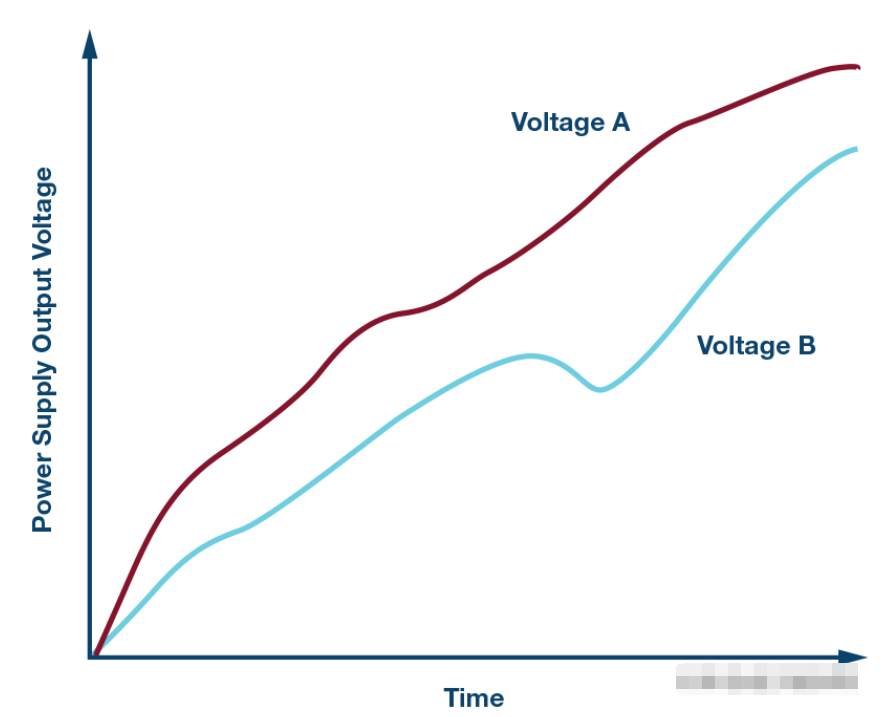

除了电压轨排序之外,一些设备还需要电压单调上升。对于单调上升,电压线性上升(不一定以恒定速率)并且在任何点都不会下降。当负载在启动期间的某些点拉电流尖峰时,可能会发生非单调电压增加。为防止电压下降,PoL 需要快速响应负载要求的任何电流尖峰。

电压 A 单调上升,电压 B 不是。(图片:模拟设备)

信封跟踪

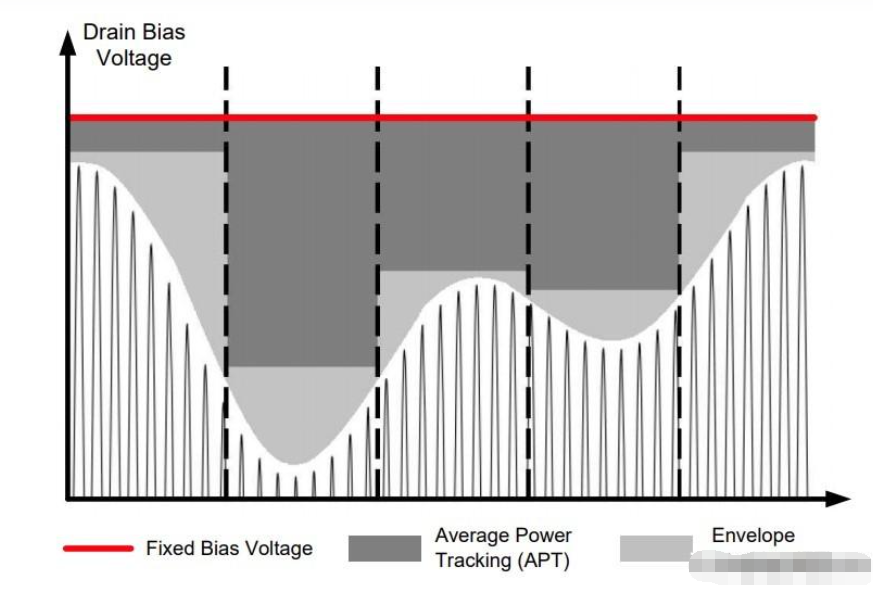

5G 等无线通信系统的信号具有较高的峰均功率比 (PAPR)。高 PAPR 值会导致功率放大器 (PA) 效率的显着降低。已开发出平均功率跟踪 (APT) 和包络跟踪 (ET),以提高 PA 在从****到手机的各种无线电应用中的功率效率。

与固定偏置电压(红线)相比,平均功率跟踪节省了由深灰色区域表示的能量,而包络跟踪将 APT 能量节省与浅灰色区域表示的额外能量节省相结合。(图片:德州仪器)

APT 提供了更简单和更粗略的调整。APT 根据相对较大的时间片改变 PA 的直流电压。PA 的输出是平均功率的函数,但经过优化以限制(或消除)削波射频信号峰值。

ET 比 APT 更快、更准确、更复杂。ET 根据 PA 的输入信号实时调整 PA 直流电压。ET 的实现需要一个专用的电源控制模块。APT 和 ET 都使用硬件和软件控制的组合来调制 PA 的电压供应,以降低整体功耗,从而减少热量产生并提高运行效率。

电力系统设计是系统设计中一个重要而复杂的部分。本常见问题解答系列从了解交流电源测量基础知识开始,然后考虑如何验证交流/直流电源性能。这个结论性的常见问题解答挖掘了在嵌入式系统中验证电力系统完整性时需要考虑的一些细微差别。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。