——Xilinx 通信高管解读“Zynq UltraScale+ RFSoC”

图: 赛灵思公司通信业务主管总监Gilles Garcia先生

RFSoC正式发货

2017年10月9日,All Programmable技术和器件的全球领先企业赛灵思公司(Xilinx)宣布其 Zynq UltraScale+ RFSoC 系列开始发货,该系列通过一个突破性的架构将 RF 信号链集成在一个单芯片SoC 中,从而为 5G 无线、有线 Remote-PHY 及其它应用的加速实现提供了可能。

实际上,今年2月赛灵思已经预发布了该芯片的架构信息,对于这么一款数字与模拟结合的高性能单芯片产品, 市场早已经是充满了期待。 那么, 此次真正推向市场的产品,和之前预发布的信息有什么不同, 是否有了更多新的功能?为此,电子产品世界编辑专访了赛灵思公司通信业务主管总监Gilles Garcia先生。

Gilles Garcia 先生表示:今年2月发布赛灵思RFSoC 架构的时候,曾经强调过目标应用就是加速5G无线的商业化部署。这次希望告诉大家的是, 第一,新发货的基于 16nm UltraScale+ MPSoC 架构的 All Programmable RFSoC 不仅可以加速5G无线的应用, 而且会在有线Remote-PHY及其它应用中扮演重要角色;第二, 此次开始供应给客户的,不是一款 RFSoC 产品,而是一个RFSoC 产品系列。此外,与今年2月的预发布相比, 2017年2月发部的只是测试芯片,可帮助客户做DAC/ADC集成,现在发货是集成后的芯片,而且还增加了SD-FEC;此外增加了一些额外的应用,诸如有线接入的DOCSIS3.1、卫星通信等。实际上,RFSoC的应用会更加广泛,现在所有需要使用DAC/ADC的应用都可能成为RFSoC的目标市场,诸如无线应用的机器学习或者光纤领域等。

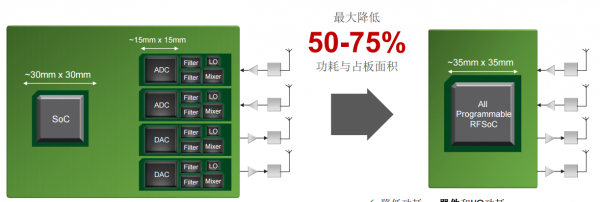

新型的 RFSoC 产品系列有很多优势,可用三句话概括:集成RF级模拟与纠错技术;可将系统的功耗和封装尺寸降低50%-70%; 跨RF信号链的完全可编程。例如,在单芯片上集成 RF 数据转换器,由于无需分立ADC和DAC器件,可将系统功耗和封装尺寸减少高达50%~70%,而且其软判决前向纠错 (SD-FEC) 内核可满足 5G 和 DOCSIS 3.1 标准要求。据悉,Zynq UltraScale+ RFSoC 系列早期试用计划现已启动,芯片样片也已经面向多家客户发货。

跨RF信号链与全可编程的相遇

一个问题是5G标准还没有确定,有线标准和其他应用的标准在演进中,RFSoC 是否能够适应未来标准和目前诸多应用?Gilles Garcia对此话题非常感兴趣,他强调,正是因为赛灵思的器件是All Programamble (全可编程)的,所以随着标准的演化,RFSoC可以跟着标准一起变化。例如LDPC编码标准如果变化的话,开发者就可以借助可编程逻辑针对LDPC的参数进行修改。赛灵思器件的优势就是可以跟着标准的变化不断变化。再例如下图里显示的很多音频、视频IP部分,都可以对它进行编程式的修改。

而且DAC/ADC也有非常大规模的配置,可以满足5G不同带宽的需求。例如DOCSIS3.1标准已经确定,赛灵思就可以为其提供相应规格的IP或者其它所需的IP。因此,“有很多运营商都在积极推动5G在2018年各种标准的部署,所以现在这个阶段如果没有FPGA、没有全可编程器件的话,5G技术就没有办法部署。”Gilles Garcia 自豪地表示。人们预计3GPP标准会在2020年确定。3GPP从15、16到17版,还会继续演化。另外在3GPP情况下,改变的并不是DAC/ADC这样的硬件,而是相关的IP,还有3GPP基带这些标准也会变化。相信随着5G各种研发的推进,赛灵思全可编程器件 Zynq Ultra Scale RFSoC 凭着其独特的优势,可以随着5G相关技术的演化发展进程不断在实践中扩大应用,并能够与时俱进适应个变化,让客户遇到标准演化时无需完全重新设计它的系统。

赛灵思提供的这些IP是收费的吗?答案是DOCSIS3.1的IP不收费,无线IP绝大多数也是免费的,还有DAC/ADC和FEC。客户购买RFSoC芯片的时候,定价已经包含了这部分。

RFSoC 发展路线图:将从16nm直接进入7nm

赛灵思已经宣布了从16nm直接进入7nm的路线图,跳过了12nm的节点。之所以选择从16nm直接到7nm,是因为赛灵思发现12/10nm节点已经无法办法满足客户对集成和功耗方面的需求,而且赛灵思现在在16nm功耗和集成方面的功能已经和12/10nm不分上下了,所以没有必要再开发12/10nm,因而直接选择了7nm作为下一个节点。今年9月赛灵思已经和台积电、ARM、Cadence 等做过一个联合发布,选择台积电作为代工合作伙伴来帮助其生产7nm芯片。

RFSoC 将打开一个全新世界

值得一提的是,RFSoC是FPGA市场上唯一达到这样集成高度的器件,包含了DAC/ADC,片上系统,可编程逻辑,FEC的硬核。那么,赛灵思昔日有很多模拟器件合作伙伴,今后和这些模拟公司的关系会怎样?

Gilles Garcia称:赛灵思进入的是一个全新的世界,这里既有竞争又有合作关系。此外客户的选择也不是我们可以决定的,有些客户可能会继续选择用传统的模拟器件。但是从赛灵思角度看,客户对于RFSoC的兴趣是巨大的。所以赛灵思也不能评价他们能怎么做,他们应该怎么做,他们会怎么做,所有相关竞争对手对赛灵思的发布应该都会做出他们的反应。在此重申一下赛灵思的战略:赛灵思非常注重倾听客户和市场的需求,例如5G无线或者有线接入的DOCSIS市场。赛灵思关注的是这个市场对于降低功耗、缩小封装尺寸等的需求。RFSoc的发布就是赛灵思对市场和客户需求做出的一个回应。所以赛灵思不会由于竞争对手一些所作所为来停止集成的步伐,目标就是回馈客户和市场的需求,更好地服务客户和市场。

图 RFSoC推出历程

小结

赛灵思在其16nm SoC基础上集成了RF信号链及IP,出炉了名为“Zynq UltraScale+ RFSoC”的芯片,目标市场是5G无线、有线Remote-PHY及其他应用。

赛灵思早在2012年推出了集成ADC/DAC的FPGA,但是被其强大的数字技术和先进制程的光芒所掩盖,人们一时忽略了此特点。但赛灵思一直没有放弃在模拟方面的研发,产品方向从通用转向一些特定目标市场,例如此次发布的RFSoC,第一次把模拟作为产品亮点,目标是即将到来的5G和有线Remote-PHY等,相信此次发布会促进这些市场的成熟。

另外,笔者对赛灵思在商业和技术上的颠覆力也表示很赞叹。从FPGA到SoC, 从SoC 再到多核的MPSoC,再到今天SoC中集成更多模拟功能的RFSoC,从做数字芯片跨界到数模混合信号芯片,赛灵思一直在扩张和跨界。也许,在Xilinx眼里,似乎只要新兴应用与客户有需求,技术就不在话下。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。