代码;

non_blocking:

module blocking(clk,a,b,c);

output [3:0] b,c;

input [3:0] a;

input clk;

reg [3:0] b,c;

always @(posedge clk)

begin

b <= a;

c <= b;

$display("Non_Blocking: a = %d, b = %d, c = %d ",a,b,c);

end

endmodulenon_blocking.vt

`timescale 1 ns/ 100 ps

module blocking_vlg_tst();

// constants

// general purpose registers

// test vector input registers

reg [3:0] a;

reg clk;

// wires

wire [3:0] b;

wire [3:0] c;

// assign statements (if any)

blocking i1 (

// port map - connection between master ports and signals/registers

.a(a),

.b(b),

.c(c),

.clk(clk)

);

initial

begin

clk = 0;

forever #50 clk = ~clk; //思考:如果在本句后还有语句,能否执行?为什么?

end

initial

begin

a = 4'h3;

$display("____________________________");

# 100 a = 4'h7;

$display("____________________________");

# 100 a = 4'hf;

$display("____________________________");

# 100 a = 4'ha;

$display("____________________________");

# 100 a = 4'h2;

$display("____________________________");

# 100 $display("____________________________");

$stop;

end

blocking blocking(clk,a,b2,c2);

endmodule仿真

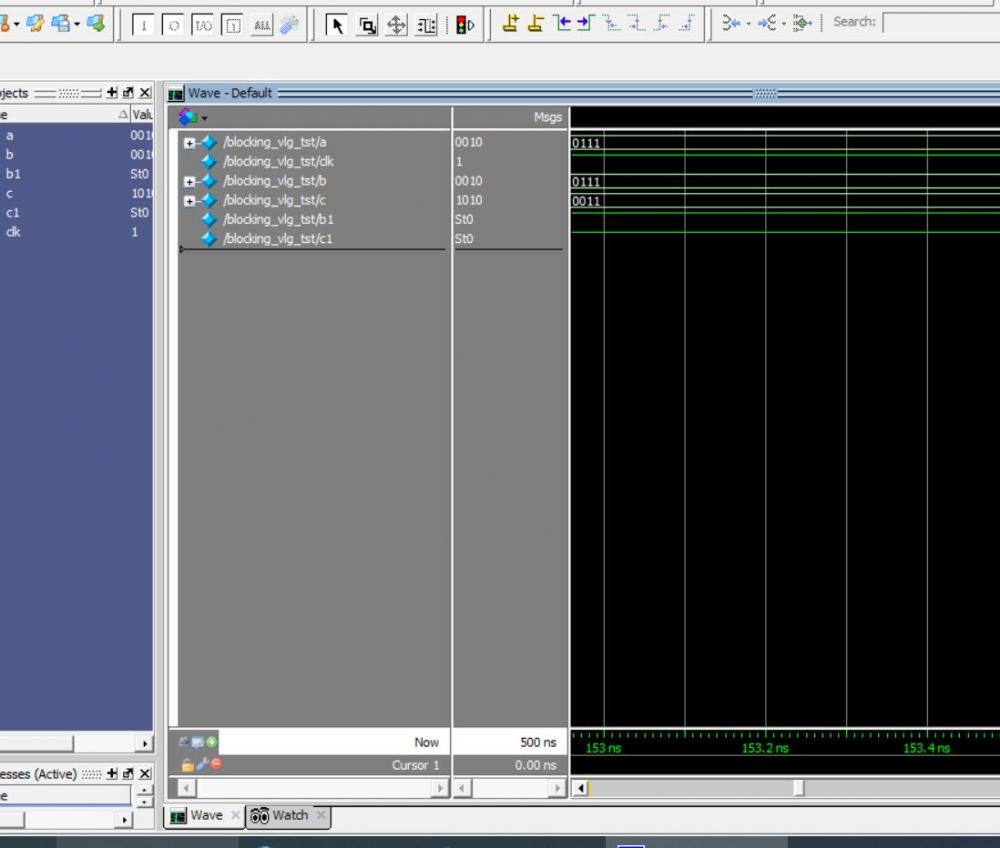

# ____________________________

# Non_Blocking: a = 3, b = x, c = x

# Non_Blocking: a = 3, b = x, c = x

# ____________________________

# Non_Blocking: a = 7, b = 3, c = x

# Non_Blocking: a = 7, b = 3, c = x

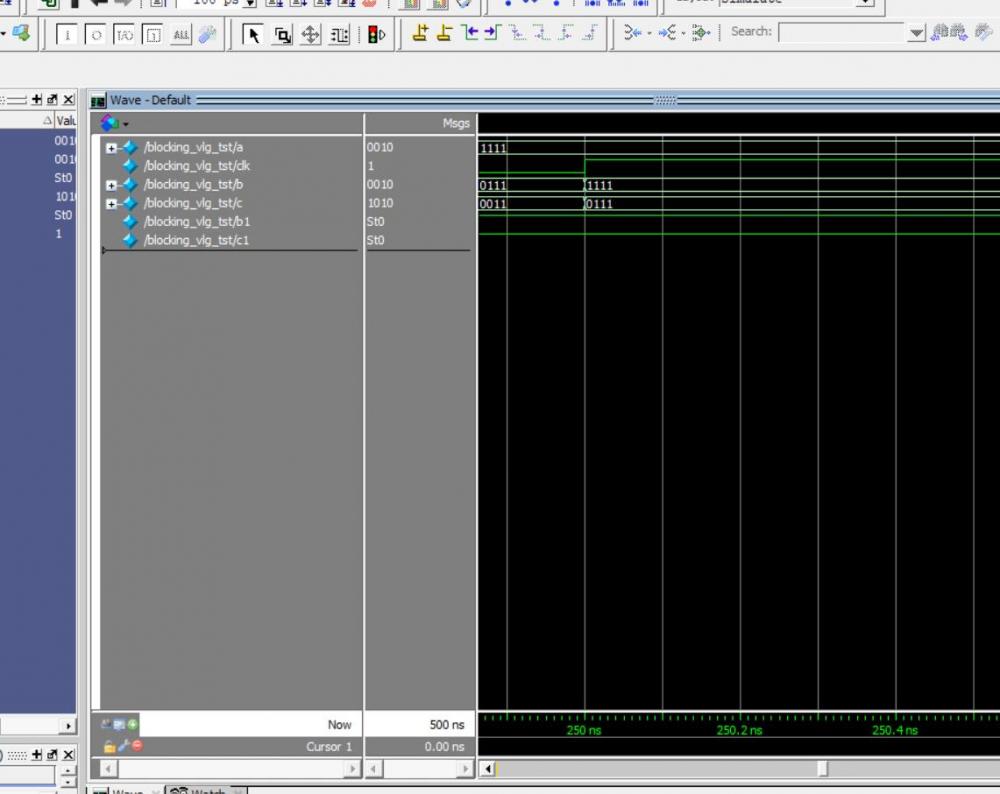

# ____________________________

# Non_Blocking: a = 15, b = 7, c = 3

# Non_Blocking: a = 15, b = 7, c = 3

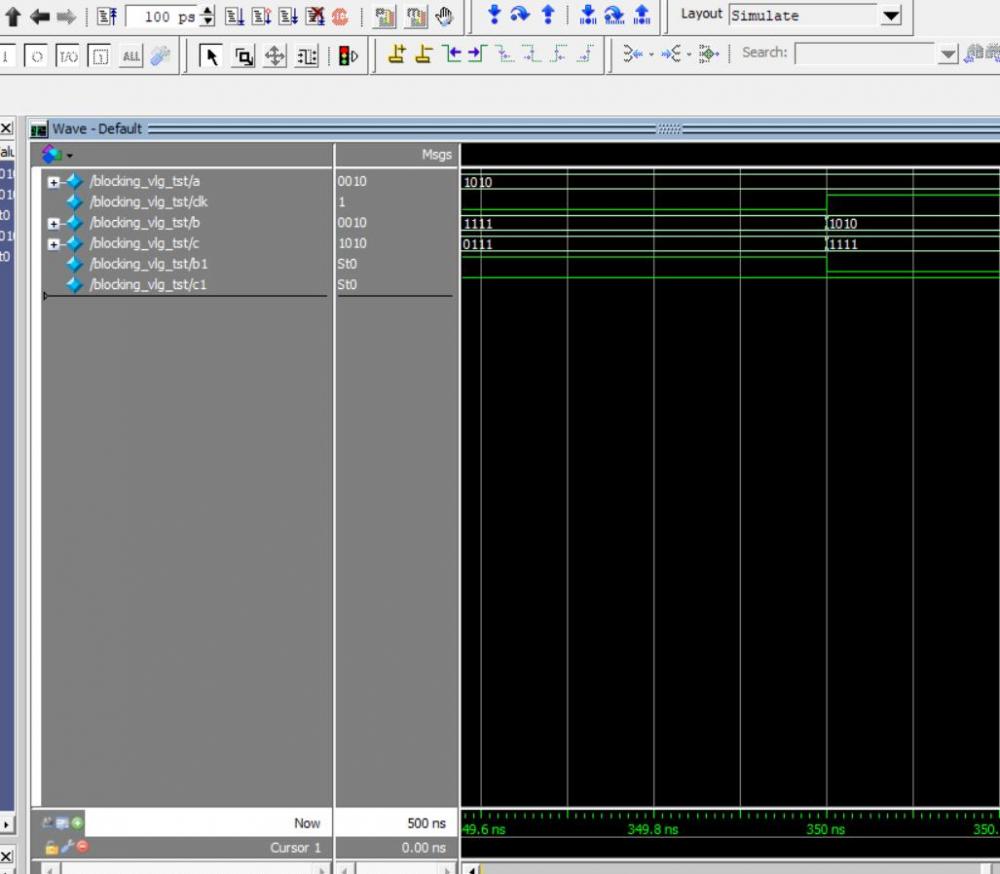

# ____________________________

# Non_Blocking: a = 10, b = 15, c = 7

# Non_Blocking: a = 10, b = 15, c = 7

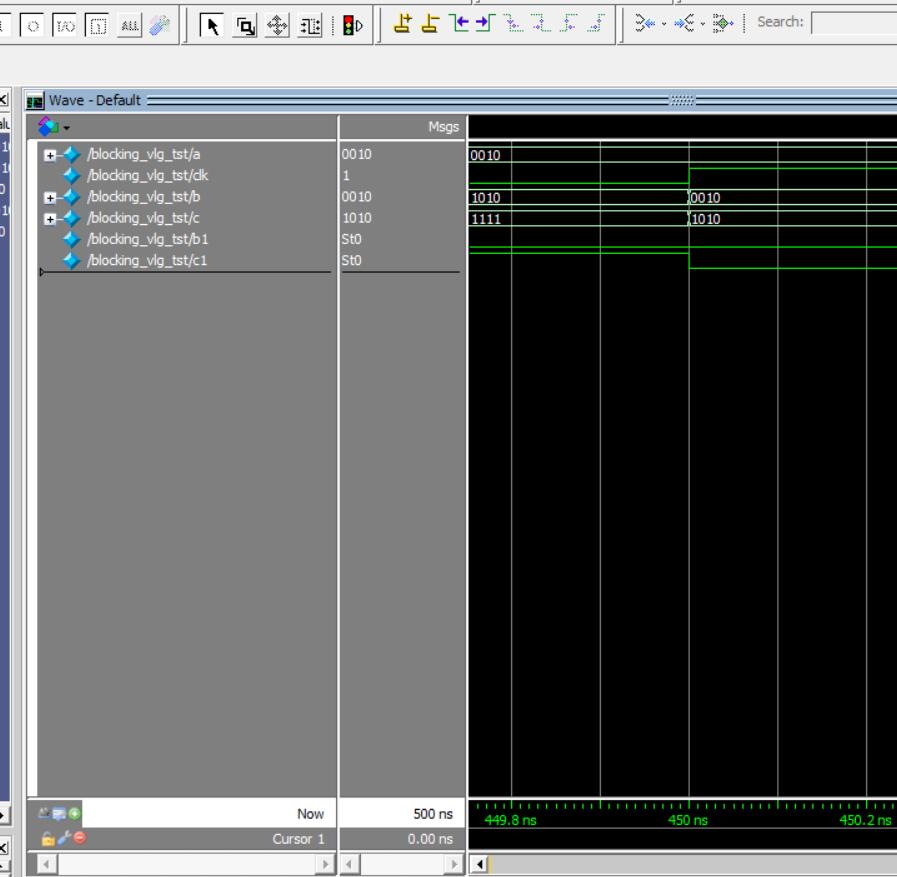

# ____________________________

# Non_Blocking: a = 2, b = 10, c = 15

# Non_Blocking: a = 2, b = 10, c = 15

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。