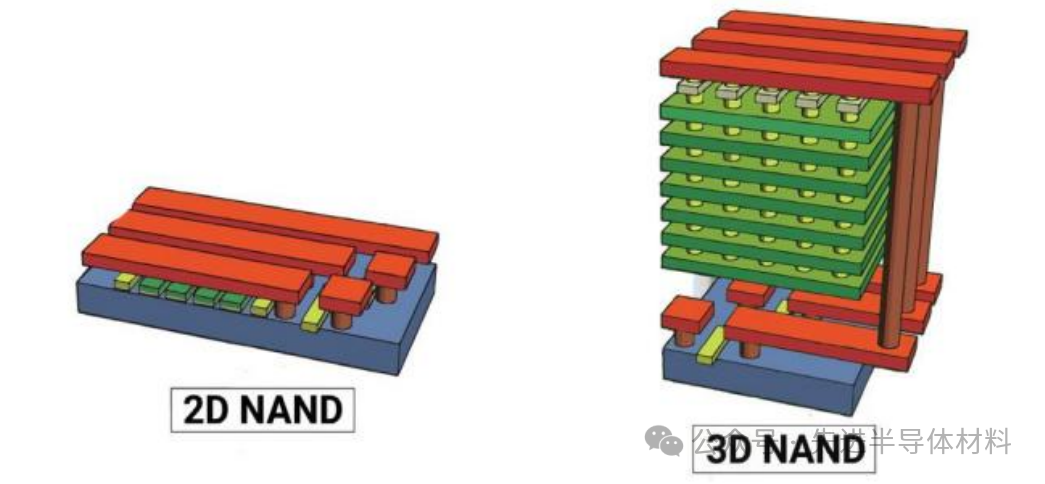

随先进制程的不断突破,刻蚀次数显著增加。在摩尔定律推动下,元器件集成度的大幅提高要求集成电路线宽不断缩小,制造工序复杂度显著增加。据 SEMI,20nm 工艺需约 1000 道工序,而 10nm 和 7nm 工艺所需工序已超 1400 道。随线宽向 10、7、5nm 升级,光刻机精度受波长限制,需采用多重模板工艺,多次薄膜沉积和刻蚀以实现更小线宽,使得刻蚀次数显著增加,20nm 工艺需刻蚀 50 次左右,而10nm 工艺超 100次,5nm 工艺超 150 次。存储芯片多层堆叠技术进步,刻蚀技术难度、次数均有所提升。2D结构存储芯片通过在平面上对晶体管尺寸进行微缩,以获得更高的存储密度而当前 2D存储器件的线宽已接近物理极限,NAND、DRAM内存芯片已进入 3D 时代。3D 结构中,增加集成度的主要方法不再是缩小单层上线宽而是增加堆叠的层数,成功解决 2D 结构增加容量的同时性能降低的问题,实现容量、速度、能效及可靠性等全方位提升。随层数的增加,芯片加工步骤也同比增加,带动上游刻蚀设备及对应耗材的需求。

随先进制程的不断突破,刻蚀次数显著增加。在摩尔定律推动下,元器件集成度的大幅提高要求集成电路线宽不断缩小,制造工序复杂度显著增加。据 SEMI,20nm 工艺需约 1000 道工序,而 10nm 和 7nm 工艺所需工序已超 1400 道。随线宽向 10、7、5nm 升级,光刻机精度受波长限制,需采用多重模板工艺,多次薄膜沉积和刻蚀以实现更小线宽,使得刻蚀次数显著增加,20nm 工艺需刻蚀 50 次左右,而10nm 工艺超 100次,5nm 工艺超 150 次。存储芯片多层堆叠技术进步,刻蚀技术难度、次数均有所提升。2D结构存储芯片通过在平面上对晶体管尺寸进行微缩,以获得更高的存储密度而当前 2D存储器件的线宽已接近物理极限,NAND、DRAM内存芯片已进入 3D 时代。3D 结构中,增加集成度的主要方法不再是缩小单层上线宽而是增加堆叠的层数,成功解决 2D 结构增加容量的同时性能降低的问题,实现容量、速度、能效及可靠性等全方位提升。随层数的增加,芯片加工步骤也同比增加,带动上游刻蚀设备及对应耗材的需求。

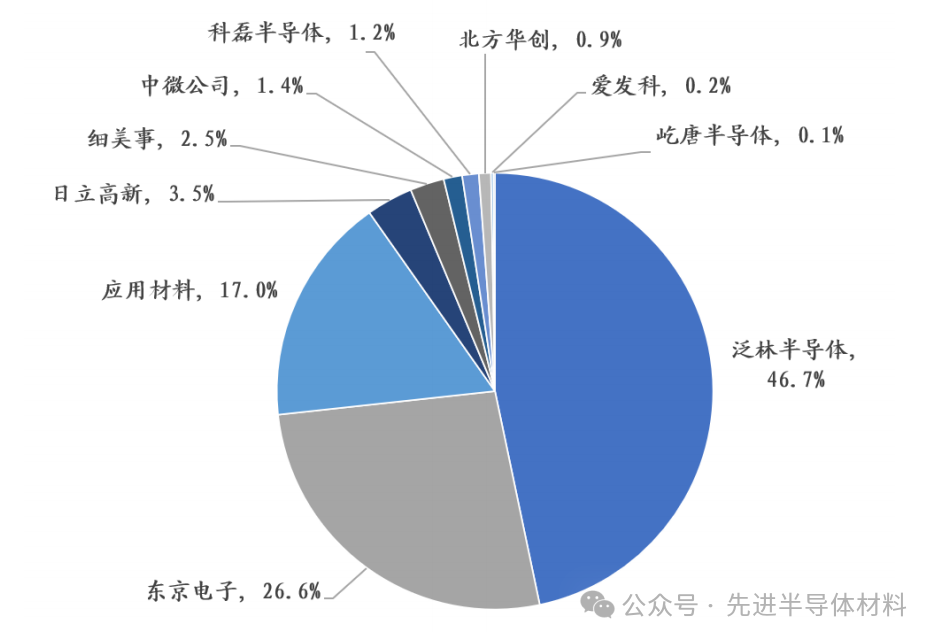

刻蚀设备市场份额情况

来源:先进半导体材料

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。