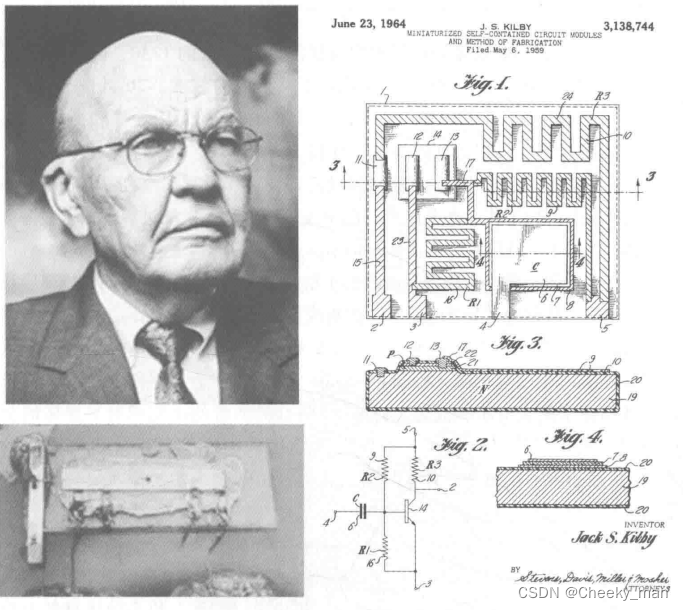

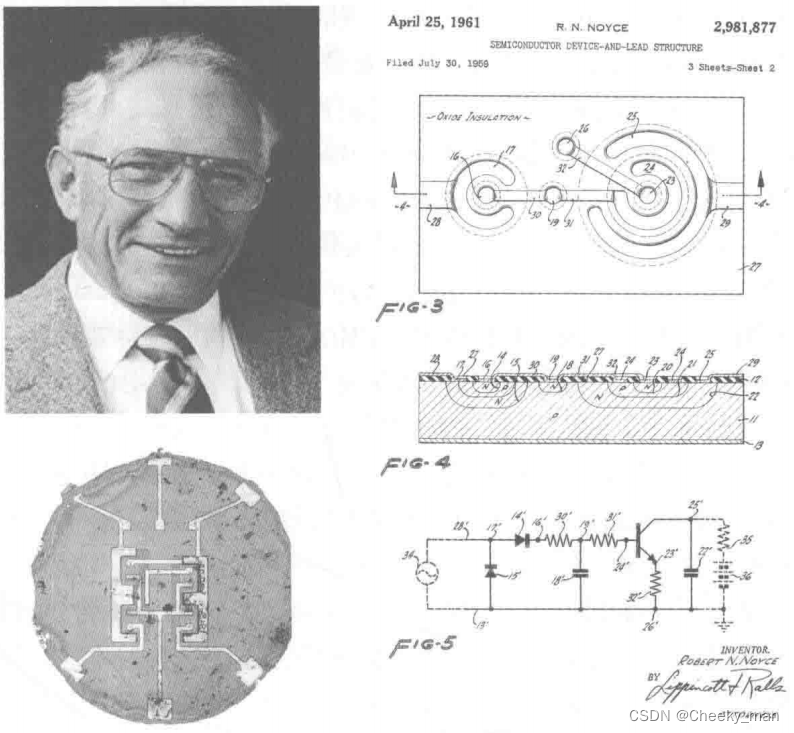

基尔比和第一个集成电路专利1959年3月6日,TI公司在纽约举行的无线电工程师学会(Institute of Radio Engineers,IRE,现电气和电子工程师协会(Institute of Electrieal and Electronics Engineers,IEEE)的前身)展览会的记者招待会上公布了“固体电路(Solid State Circuit)",即集成电路(Integrated Circuit,IC)的发明。在TI公司申请了集成电路发明专利的5个月以后,即1959年7月30日,仙童公司(Fairchild Co.)的诺伊斯(Robert N. Noyce)申请了基于硅平面工艺的集成电路专利(专利号为No.2981877,批准日期为1961年4月25日)。诺伊斯的发明更适合集成电路的大批量生产。

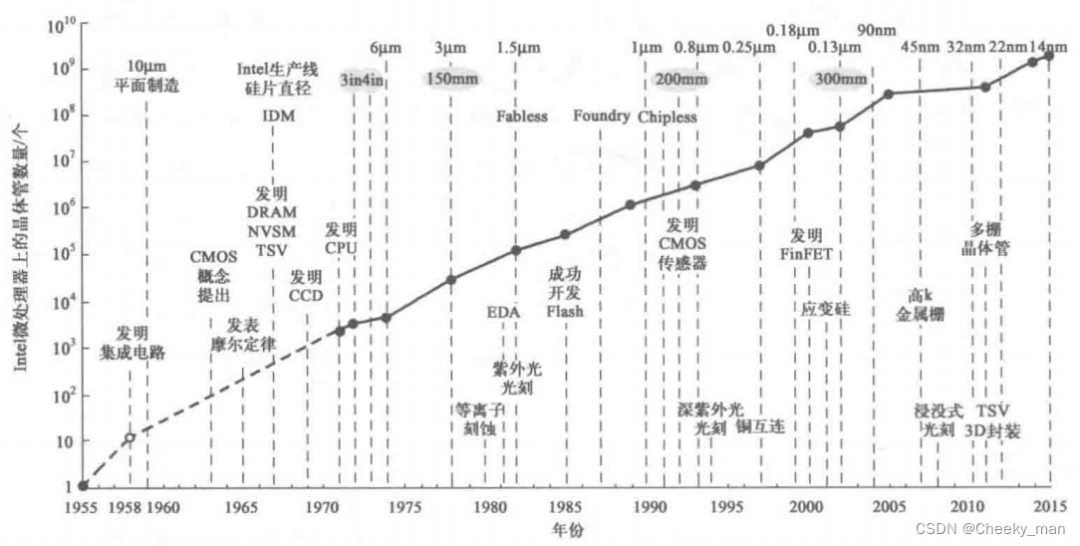

基尔比和第一个集成电路专利1959年3月6日,TI公司在纽约举行的无线电工程师学会(Institute of Radio Engineers,IRE,现电气和电子工程师协会(Institute of Electrieal and Electronics Engineers,IEEE)的前身)展览会的记者招待会上公布了“固体电路(Solid State Circuit)",即集成电路(Integrated Circuit,IC)的发明。在TI公司申请了集成电路发明专利的5个月以后,即1959年7月30日,仙童公司(Fairchild Co.)的诺伊斯(Robert N. Noyce)申请了基于硅平面工艺的集成电路专利(专利号为No.2981877,批准日期为1961年4月25日)。诺伊斯的发明更适合集成电路的大批量生产。 诺伊斯和平面集成电路专利2000年,基尔比被授予诺贝尔物理学奖。诺贝尔奖评审委员会曾评价基尔比“为现代信息技术奠定了基础”。遗憾的是,诺贝尔奖不颁给已故之人,而诺伊斯于1990年6月3日辞世,因此未能获此殊荣。当我们看到第一枚集成电路样品时,我们会对它的简陋与粗糙感到讶异,但其中蕴含的博大与精深的智慧却永远值得我们深思。1.4 集成电路产业中信息获取、存储与处理的里程碑1.4.1 集成电路在信息获取领域的发展图像传感器(Imaging Sensor)和微机电系统(Micro-Electro-Mechanical System,MEMS)是集成电路在信息获取领域取得重要成果的两个里程碑。1969年,美国贝尔实验室(Bell Labs)的威拉德·博伊尔(Willard S.Boyle)和乔治·史密斯(George E. Smith)发明的电荷耦合器件(Charge Coupled Device,CCD)解决了光学影像转化为数字信号的问题。2009年,两位发明人获诺贝尔物理学奖。1992年,美国喷气推进实验室(Jet Propulsion Laboratory,JPL)的埃里克·弗萨姆(EricFossum)发明了CMOS有源像素传感器(CMOS Active Pixel Sensor)。与CCD相比,CMOS具有体积小,耗电量不到CCD的1/10,售价比CD便宜1/3的优点。当前,数码相机(包括手机)的感光装置主要是CMOS图像传感器。1.4.2 集成电路在微机电系统领域的发展微机电系统的发展始于硅微压力传感器。1959年,理查德·菲利普斯·费曼(Richard P.Feynman)提出了微型机械的设想。1987年,加州大学伯克利分校研制出转子直径为60~12μm的电动机。微机电系统可以集成速度、温度、湿度、高度、声音、压力、方位、气体等更多的传感器,使人们通过直觉感受到的模拟信息(快慢、冷热、干湿、力度)能够精确地数字化。被传感器采集的数据在MEMS内部进行存储和处理后,既可以输出到内部的执行器,如陀螺、电动机,也可以与外部设备进行数据交换。1.4.3 集成电路在存储领域的发展半导体存储器最大的贡献是解决了海量信息的存储问题。人类最初存储信息的媒介是大脑,传播信息的方式是口传心授。其后,人类历史发展的信息存储于自然界的物体(如岩石、龟甲、竹简、羊皮)、人工制造的器物(如铜器、陶器)和建筑物之中。纸张是人类用于存储信息最广也是最久远的媒体。电子计算机的存储器最初是机电装置(如继电器),后为磁性介质(如磁鼓、磁带、磁芯)。但磁性介质依然存在体积大、质量大、存储量小的弊端。继1963年美国仙童公司的弗朗克·万拉斯(Frank Wanlass)和萨支唐(Chi-Tang Sah)提出金属氧化物半导体(Metal-Oxide-Semiconductor,MOS)概念之后,在1967年7月,同时发明了两种半导体存储器∶一是在IBM工作的登纳德(Robert Dennard)发明的动态随机存取存储器(Dynamic Random Access Memory,DRAM),二是在美国贝尔实验室工作的华裔科学家施敏和韩裔科学家姜大元发明的非易失性半导体存储器(Non-volatile Semiconductor Memory,NVSM)。1969年,Intel研制成功64bit双极静态随机存取存储器(SRAM)芯片C3101,开创了半导体存储器的先河。1984年,根据NVSM原型,日本东芝公司的舛冈富士雄(Fujio Masuoka)开发出了闪速存储器(Flash Memory)。DRAM保存数据的时间很短,需要定时刷新,一般作为计算机的内存。快闪存储器可以长期保存数据,一般作为计算机的外存。1970年,Intel采用12μm工艺开发的1Kbit MOS DRAM(C1103型)问世。1Kbit DRAM的商品化使得半导体存储器迅速在计算机中取代了磁芯存储器。今天,DRAM的存储量已经达到10^9bit数量级。1988年,Intel率先生产了256Kbit 闪存芯片并将其投放市场。今天,由闪存构成的固态硬盘(Solid State Drive,SSD)的最大容量已经达到10^13bit数量级,大有取代机械硬盘(Hard Disk Drive,HDD)的趋势。1.4.4 集成电路在处理器领域的发展最早的数据处理器可以追溯到算筹、算盘、计算尺、机械计算机以及后来的电子管计算机和晶体管计算机,虽然后者的计算速度大大超过了前者,但其体积、质量与功耗难以为一般企业、家庭,更不用说个人所接受。1971年,Intel的霍夫(Hoff)发明了型号为4004的中央处理器(Central Processing Unit,CPU),集成电路作为最重要的角色登上了信息处理的历史舞台。迄今,微处理器(Microprocessor Unit,MPU)已经成为所有电子设备不可或缺的核心部件。1.5 集成电路材料发展的里程碑1.5.1 第一代半导体材料:以锗和硅为主最早的半导体材料是锗。世界第一个晶体管和第一块集成电路的材料均是锗。1886年,德国化学家温克勒(C.A.Winkler)首先制备出锗,为纪念其祖国,他把这种新元素命名为Germanium,来源于德国的拉丁文名称“Germania”。1950年,美国人蒂尔(G.K.Teal)和里特尔(J.B.Little)采用切克劳斯基(J.Czochralski)法(又称直拉法或CZ法)拉出锗单晶。锗的热导率较低,为64W/(m·K),用锗制造的器件只能工作在90℃以下的环境,高于90℃时,锗器件的漏电流明显增大;锗的熔点只有937℃,难以承受诸如掺杂、激活、退火等高温工艺过程;同时,锗的氧化物溶于水,结构不稳定,无法制成MOS器件;更重要的是,锗的机械性能较差,锗单晶的直径不宜很大,锗晶片的加工与运输也存在一定的安全问题。1952年,蒂尔和比勒(E.Buehler)用直拉法拉出硅单晶。随后,德州仪器(TI)于1954年成功制造了第一支硅晶体管。由于硅具备禁带宽度大(为1.106eV)、热导率高(为145W/(m·K))、硅氧化物(SiO2)是性能最好的介电绝缘材料、硅是地球上最丰富的元素之一(约占地壳质量的26%)等一系列优势,20世纪60年代以后,硅成为半导体功能材料的主流。1.5.2 第二代半导体材料:以砷化镓(GaAs)等为主以砷化镓(GaAs)、磷化铟(InP)、锑化铟(InSb)和硫化镉(CdS)等Ⅲ-V族化合物材料为主,适用于制作高速、高频、大功率以及发光电子器件,是制作高性能微波、毫米波器件以及发光器件的优良材料,被广泛应用于卫星通信、移动通信、光通信和全球定位系统(Global Positioning System,GPS)等领域。1.5.3 第三代半导体材料:以碳化硅(SiC)等为主主要指以碳化硅(SiC)、氮化镓(GaN)、氧化锌(ZnO)和氮化铝(AIN)等为代表的宽禁带(禁带宽度大于2.2eV)半导体材料。第三代半导体材料具有禁带宽度大、击穿电场高、功率密度大(氮化镓的功率密度是砷化镓的10~30倍)、热导率高、电子饱和速率高及抗辐射能力高等优秀品质,因而更适合制作高温、高频、抗辐射、大功率器件和半导体激光器等。目前,较为成熟的第三代半导体材料是碳化硅和氮化镓,碳化硅比氧化镓更成熟一些。1.5.4 新材料随着新器件的开发,更多高k介质(High-k Dielectric)材料(Mg、Ca、Sr、Ba、La、Hf等)、金属栅材料(Al、Ni、镧系金属、稀土金属等)、互连材料(Ti、Ta、W等)、存储器材料(各种过渡金属氧化物,如BaTiO3、SrTiO3、TiO2、ZrO2、NiO、MoO3、V2O5、WO3、ZnO等)、外延和衬底材料(应变硅,FD-SOI等)、碳基材料(碳纳米管、石墨烯等)的研究正在广泛展开。例如,FinFET(Fin Field Effect Transistor,鳍式场效应晶体)工艺将采用Ⅲ-V族材料来增加载流子的迁移率,在互连结构中采用钛、钴或钉构成连线及氮化钛作为阻挡层材料。1.6 集成电路制造发展的里程碑广义的集成电路制造主要包括设计、制造和封测三个方面。1.6.1 集成电路的设计集成电路最初的设计方法是全手工设计,如手工画图,人工刻制曝光用的多层掩模等。人工设计仅适用于小规模集成电路。20世纪70年代,第一代集成电路计算机辅助设计(Integrated Circuit Computer Aided Design,ICAD)系统问世。由于当时的计算机存储量不够大,运算速度也不够快,因此ICCAD工具只能简单处理版图级设计问题。20世纪70年代末,出现了仿真和自动布局布线工具,提高了集成电路的设计效率。1983年,工作站(Workstation)在市场上崭露头角,有力地支持了ICCAD技术的发展,出现了第二代ICCAD系统,增加了逻辑级设计功能。20世纪90年代,ICCAD系统进入第三代,将行为级设计以硬件描述语言(Hardware Description Language,HDL)的方式纳入自动化设计的范畴。进入21世纪后,集成电路设计向可制造设计(Design for Manufactory,DFM)方向发展,其重要技术方向有软硬件协同设计、IP库、低功耗设计、可靠性设计,以及系统芯片(System on Chip,SoC)和系统级封装(System in Package,SiP)。1.6.2 集成电路的制造集成电路制造是一个在特定薄膜上制造特定图形的过程。其中的氧化、外延、掺杂(扩散、离子注入)、沉积(物理气相沉积、化学气相沉积)等工艺为薄膜制造工艺,光刻(曝光和刻蚀)工艺为图形制作工艺。曝光和刻蚀是是集成电路完成图形制作的最核心工艺,缩小加工尺寸首先要减小曝光光源的波长。20世纪70年代中期以前,曝光光源为汞灯,汞灯是一种多波长的光源,其波长范围为400~700mm。1982年,曝光光源改进为紫外光(UItraviolet,UV)g线(波长为436nm)和i线(波长为365nm)。1994年,曝光光源波长进入深紫外光领域(DUV),主要为准分子激光KrF(波长为248mm)和ArF(波长为193nm)。2003年12月,荷兰ASML(Advanced Semiconductor Material Lithography)公司发布了全球首套商用浸没式光刻(Immersion Lithography)设备,将纯净水充满投影物镜最后一个透镜的下表面与硅片之间,使得曝光光源的有效波长缩短,将193mm光刻延伸到32mm CMOS技术节点。此外,利用双曝光/成像(Double Exposure/Double Patteming)技术,将193nm浸没式光刻技术扩展到了10mm/7mm技术节点。经过一定图形曝光后的薄膜,还必须去除不需要的部分才能得到所希望的图形,这就是刻蚀工艺。最初的刻蚀技术是湿法刻蚀,由于是各向同性腐蚀,所以对图形尺寸的控制性较差。1980年以后,刻蚀技术进入干法刻蚀的时代,其中包括等离子刻蚀和反应离子刻蚀(Reactive Ion Etching,RIE),后者是当前主流的刻蚀技术。当所有的晶体管通过薄膜技术和光刻技术在硅片上制作完成时,还必须采用互连技术将上百万乃至数十亿个晶体管按照所设计的规则连接起来才能形成真正的电路。最初的互连材料是铝,研究表明,0.25μm工艺(铝导线,SiO2介质)的情况下,由互连产生的延迟已经超过门电路的延迟。1997年,IBM 宣布推出了采用铜(电导率为59.6×10's/m)互连技术的芯片,这就是著名的镶嵌工艺。1.6.3 集成电路的封装整机或系统是集成电路与最终消费者之间的界面,集成电路只有通过在整机或系统中的应用才能体现其价值;封装是集成电路芯片与整机或系统的界面,只有经过封装后的芯片才能装入系统,并在系统中发挥应有的效用。最初的集成电路封装沿用了晶体管的TO(Transistor Outline)封装形式。20世纪60年代中期,双列直插式引脚封装(Double In-Line Package,DIP)成为集成电路封装的主流。20世纪80年代,表面贴装技术(Surface Moumt Technology,SMT)得到长足发展,出现了多种封装形式,如塑料有引线片式载体(Plastic Ieaded Chip Carrier,PLCC)封装、塑料四面引线扁平封装(Plastic Quad Flat Package,PQFP)等。20世纪80年代至90年代,集成电路封装引脚开始由周边型向面阵型发展,如针栅阵列(Pin Grid Array,PGA)封装。自20世纪90年代的球栅阵列(Ball Grid Array,BGA)封装开始,封装的“插装”概念被“贴装”所颠覆,“管脚”被“焊球”所替代。20世纪末,芯片尺寸封装(Chip Size Package,CSP)解决了芯片面积小而封装面积大的矛盾,引发了封装技术的革命。今后集成电路封装将向系统级封装(System in Package,SiP)的方向发展。3D封装中最重要的技术是硅通孔(Through Silicon Vias,TSV),该技术基于IBM的Merlin Smith和Emanuel Stem于1964年的发明专利,2010年以后开始在集成电路封装中得到应用。集成电路制造技术中的另一个发展趋势是硅片直径不断增大。以Intel生产线为例,1972年硅片直径为3in,1992年为200mm,2002年Intel建立了第一条300mm硅片的生产线。综上所述,集成电路制造技术发展的重要里程碑如图所示。

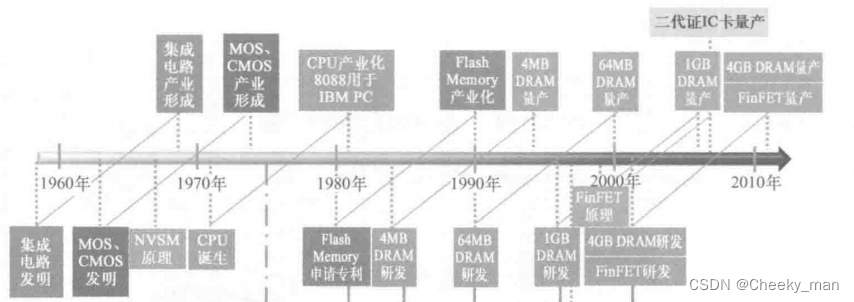

诺伊斯和平面集成电路专利2000年,基尔比被授予诺贝尔物理学奖。诺贝尔奖评审委员会曾评价基尔比“为现代信息技术奠定了基础”。遗憾的是,诺贝尔奖不颁给已故之人,而诺伊斯于1990年6月3日辞世,因此未能获此殊荣。当我们看到第一枚集成电路样品时,我们会对它的简陋与粗糙感到讶异,但其中蕴含的博大与精深的智慧却永远值得我们深思。1.4 集成电路产业中信息获取、存储与处理的里程碑1.4.1 集成电路在信息获取领域的发展图像传感器(Imaging Sensor)和微机电系统(Micro-Electro-Mechanical System,MEMS)是集成电路在信息获取领域取得重要成果的两个里程碑。1969年,美国贝尔实验室(Bell Labs)的威拉德·博伊尔(Willard S.Boyle)和乔治·史密斯(George E. Smith)发明的电荷耦合器件(Charge Coupled Device,CCD)解决了光学影像转化为数字信号的问题。2009年,两位发明人获诺贝尔物理学奖。1992年,美国喷气推进实验室(Jet Propulsion Laboratory,JPL)的埃里克·弗萨姆(EricFossum)发明了CMOS有源像素传感器(CMOS Active Pixel Sensor)。与CCD相比,CMOS具有体积小,耗电量不到CCD的1/10,售价比CD便宜1/3的优点。当前,数码相机(包括手机)的感光装置主要是CMOS图像传感器。1.4.2 集成电路在微机电系统领域的发展微机电系统的发展始于硅微压力传感器。1959年,理查德·菲利普斯·费曼(Richard P.Feynman)提出了微型机械的设想。1987年,加州大学伯克利分校研制出转子直径为60~12μm的电动机。微机电系统可以集成速度、温度、湿度、高度、声音、压力、方位、气体等更多的传感器,使人们通过直觉感受到的模拟信息(快慢、冷热、干湿、力度)能够精确地数字化。被传感器采集的数据在MEMS内部进行存储和处理后,既可以输出到内部的执行器,如陀螺、电动机,也可以与外部设备进行数据交换。1.4.3 集成电路在存储领域的发展半导体存储器最大的贡献是解决了海量信息的存储问题。人类最初存储信息的媒介是大脑,传播信息的方式是口传心授。其后,人类历史发展的信息存储于自然界的物体(如岩石、龟甲、竹简、羊皮)、人工制造的器物(如铜器、陶器)和建筑物之中。纸张是人类用于存储信息最广也是最久远的媒体。电子计算机的存储器最初是机电装置(如继电器),后为磁性介质(如磁鼓、磁带、磁芯)。但磁性介质依然存在体积大、质量大、存储量小的弊端。继1963年美国仙童公司的弗朗克·万拉斯(Frank Wanlass)和萨支唐(Chi-Tang Sah)提出金属氧化物半导体(Metal-Oxide-Semiconductor,MOS)概念之后,在1967年7月,同时发明了两种半导体存储器∶一是在IBM工作的登纳德(Robert Dennard)发明的动态随机存取存储器(Dynamic Random Access Memory,DRAM),二是在美国贝尔实验室工作的华裔科学家施敏和韩裔科学家姜大元发明的非易失性半导体存储器(Non-volatile Semiconductor Memory,NVSM)。1969年,Intel研制成功64bit双极静态随机存取存储器(SRAM)芯片C3101,开创了半导体存储器的先河。1984年,根据NVSM原型,日本东芝公司的舛冈富士雄(Fujio Masuoka)开发出了闪速存储器(Flash Memory)。DRAM保存数据的时间很短,需要定时刷新,一般作为计算机的内存。快闪存储器可以长期保存数据,一般作为计算机的外存。1970年,Intel采用12μm工艺开发的1Kbit MOS DRAM(C1103型)问世。1Kbit DRAM的商品化使得半导体存储器迅速在计算机中取代了磁芯存储器。今天,DRAM的存储量已经达到10^9bit数量级。1988年,Intel率先生产了256Kbit 闪存芯片并将其投放市场。今天,由闪存构成的固态硬盘(Solid State Drive,SSD)的最大容量已经达到10^13bit数量级,大有取代机械硬盘(Hard Disk Drive,HDD)的趋势。1.4.4 集成电路在处理器领域的发展最早的数据处理器可以追溯到算筹、算盘、计算尺、机械计算机以及后来的电子管计算机和晶体管计算机,虽然后者的计算速度大大超过了前者,但其体积、质量与功耗难以为一般企业、家庭,更不用说个人所接受。1971年,Intel的霍夫(Hoff)发明了型号为4004的中央处理器(Central Processing Unit,CPU),集成电路作为最重要的角色登上了信息处理的历史舞台。迄今,微处理器(Microprocessor Unit,MPU)已经成为所有电子设备不可或缺的核心部件。1.5 集成电路材料发展的里程碑1.5.1 第一代半导体材料:以锗和硅为主最早的半导体材料是锗。世界第一个晶体管和第一块集成电路的材料均是锗。1886年,德国化学家温克勒(C.A.Winkler)首先制备出锗,为纪念其祖国,他把这种新元素命名为Germanium,来源于德国的拉丁文名称“Germania”。1950年,美国人蒂尔(G.K.Teal)和里特尔(J.B.Little)采用切克劳斯基(J.Czochralski)法(又称直拉法或CZ法)拉出锗单晶。锗的热导率较低,为64W/(m·K),用锗制造的器件只能工作在90℃以下的环境,高于90℃时,锗器件的漏电流明显增大;锗的熔点只有937℃,难以承受诸如掺杂、激活、退火等高温工艺过程;同时,锗的氧化物溶于水,结构不稳定,无法制成MOS器件;更重要的是,锗的机械性能较差,锗单晶的直径不宜很大,锗晶片的加工与运输也存在一定的安全问题。1952年,蒂尔和比勒(E.Buehler)用直拉法拉出硅单晶。随后,德州仪器(TI)于1954年成功制造了第一支硅晶体管。由于硅具备禁带宽度大(为1.106eV)、热导率高(为145W/(m·K))、硅氧化物(SiO2)是性能最好的介电绝缘材料、硅是地球上最丰富的元素之一(约占地壳质量的26%)等一系列优势,20世纪60年代以后,硅成为半导体功能材料的主流。1.5.2 第二代半导体材料:以砷化镓(GaAs)等为主以砷化镓(GaAs)、磷化铟(InP)、锑化铟(InSb)和硫化镉(CdS)等Ⅲ-V族化合物材料为主,适用于制作高速、高频、大功率以及发光电子器件,是制作高性能微波、毫米波器件以及发光器件的优良材料,被广泛应用于卫星通信、移动通信、光通信和全球定位系统(Global Positioning System,GPS)等领域。1.5.3 第三代半导体材料:以碳化硅(SiC)等为主主要指以碳化硅(SiC)、氮化镓(GaN)、氧化锌(ZnO)和氮化铝(AIN)等为代表的宽禁带(禁带宽度大于2.2eV)半导体材料。第三代半导体材料具有禁带宽度大、击穿电场高、功率密度大(氮化镓的功率密度是砷化镓的10~30倍)、热导率高、电子饱和速率高及抗辐射能力高等优秀品质,因而更适合制作高温、高频、抗辐射、大功率器件和半导体激光器等。目前,较为成熟的第三代半导体材料是碳化硅和氮化镓,碳化硅比氧化镓更成熟一些。1.5.4 新材料随着新器件的开发,更多高k介质(High-k Dielectric)材料(Mg、Ca、Sr、Ba、La、Hf等)、金属栅材料(Al、Ni、镧系金属、稀土金属等)、互连材料(Ti、Ta、W等)、存储器材料(各种过渡金属氧化物,如BaTiO3、SrTiO3、TiO2、ZrO2、NiO、MoO3、V2O5、WO3、ZnO等)、外延和衬底材料(应变硅,FD-SOI等)、碳基材料(碳纳米管、石墨烯等)的研究正在广泛展开。例如,FinFET(Fin Field Effect Transistor,鳍式场效应晶体)工艺将采用Ⅲ-V族材料来增加载流子的迁移率,在互连结构中采用钛、钴或钉构成连线及氮化钛作为阻挡层材料。1.6 集成电路制造发展的里程碑广义的集成电路制造主要包括设计、制造和封测三个方面。1.6.1 集成电路的设计集成电路最初的设计方法是全手工设计,如手工画图,人工刻制曝光用的多层掩模等。人工设计仅适用于小规模集成电路。20世纪70年代,第一代集成电路计算机辅助设计(Integrated Circuit Computer Aided Design,ICAD)系统问世。由于当时的计算机存储量不够大,运算速度也不够快,因此ICCAD工具只能简单处理版图级设计问题。20世纪70年代末,出现了仿真和自动布局布线工具,提高了集成电路的设计效率。1983年,工作站(Workstation)在市场上崭露头角,有力地支持了ICCAD技术的发展,出现了第二代ICCAD系统,增加了逻辑级设计功能。20世纪90年代,ICCAD系统进入第三代,将行为级设计以硬件描述语言(Hardware Description Language,HDL)的方式纳入自动化设计的范畴。进入21世纪后,集成电路设计向可制造设计(Design for Manufactory,DFM)方向发展,其重要技术方向有软硬件协同设计、IP库、低功耗设计、可靠性设计,以及系统芯片(System on Chip,SoC)和系统级封装(System in Package,SiP)。1.6.2 集成电路的制造集成电路制造是一个在特定薄膜上制造特定图形的过程。其中的氧化、外延、掺杂(扩散、离子注入)、沉积(物理气相沉积、化学气相沉积)等工艺为薄膜制造工艺,光刻(曝光和刻蚀)工艺为图形制作工艺。曝光和刻蚀是是集成电路完成图形制作的最核心工艺,缩小加工尺寸首先要减小曝光光源的波长。20世纪70年代中期以前,曝光光源为汞灯,汞灯是一种多波长的光源,其波长范围为400~700mm。1982年,曝光光源改进为紫外光(UItraviolet,UV)g线(波长为436nm)和i线(波长为365nm)。1994年,曝光光源波长进入深紫外光领域(DUV),主要为准分子激光KrF(波长为248mm)和ArF(波长为193nm)。2003年12月,荷兰ASML(Advanced Semiconductor Material Lithography)公司发布了全球首套商用浸没式光刻(Immersion Lithography)设备,将纯净水充满投影物镜最后一个透镜的下表面与硅片之间,使得曝光光源的有效波长缩短,将193mm光刻延伸到32mm CMOS技术节点。此外,利用双曝光/成像(Double Exposure/Double Patteming)技术,将193nm浸没式光刻技术扩展到了10mm/7mm技术节点。经过一定图形曝光后的薄膜,还必须去除不需要的部分才能得到所希望的图形,这就是刻蚀工艺。最初的刻蚀技术是湿法刻蚀,由于是各向同性腐蚀,所以对图形尺寸的控制性较差。1980年以后,刻蚀技术进入干法刻蚀的时代,其中包括等离子刻蚀和反应离子刻蚀(Reactive Ion Etching,RIE),后者是当前主流的刻蚀技术。当所有的晶体管通过薄膜技术和光刻技术在硅片上制作完成时,还必须采用互连技术将上百万乃至数十亿个晶体管按照所设计的规则连接起来才能形成真正的电路。最初的互连材料是铝,研究表明,0.25μm工艺(铝导线,SiO2介质)的情况下,由互连产生的延迟已经超过门电路的延迟。1997年,IBM 宣布推出了采用铜(电导率为59.6×10's/m)互连技术的芯片,这就是著名的镶嵌工艺。1.6.3 集成电路的封装整机或系统是集成电路与最终消费者之间的界面,集成电路只有通过在整机或系统中的应用才能体现其价值;封装是集成电路芯片与整机或系统的界面,只有经过封装后的芯片才能装入系统,并在系统中发挥应有的效用。最初的集成电路封装沿用了晶体管的TO(Transistor Outline)封装形式。20世纪60年代中期,双列直插式引脚封装(Double In-Line Package,DIP)成为集成电路封装的主流。20世纪80年代,表面贴装技术(Surface Moumt Technology,SMT)得到长足发展,出现了多种封装形式,如塑料有引线片式载体(Plastic Ieaded Chip Carrier,PLCC)封装、塑料四面引线扁平封装(Plastic Quad Flat Package,PQFP)等。20世纪80年代至90年代,集成电路封装引脚开始由周边型向面阵型发展,如针栅阵列(Pin Grid Array,PGA)封装。自20世纪90年代的球栅阵列(Ball Grid Array,BGA)封装开始,封装的“插装”概念被“贴装”所颠覆,“管脚”被“焊球”所替代。20世纪末,芯片尺寸封装(Chip Size Package,CSP)解决了芯片面积小而封装面积大的矛盾,引发了封装技术的革命。今后集成电路封装将向系统级封装(System in Package,SiP)的方向发展。3D封装中最重要的技术是硅通孔(Through Silicon Vias,TSV),该技术基于IBM的Merlin Smith和Emanuel Stem于1964年的发明专利,2010年以后开始在集成电路封装中得到应用。集成电路制造技术中的另一个发展趋势是硅片直径不断增大。以Intel生产线为例,1972年硅片直径为3in,1992年为200mm,2002年Intel建立了第一条300mm硅片的生产线。综上所述,集成电路制造技术发展的重要里程碑如图所示。 集成电路制造技术发展的重要里程碑二、集成电路产业的发展规律2.1 半导体产品制造技术约10年一代的技术进步

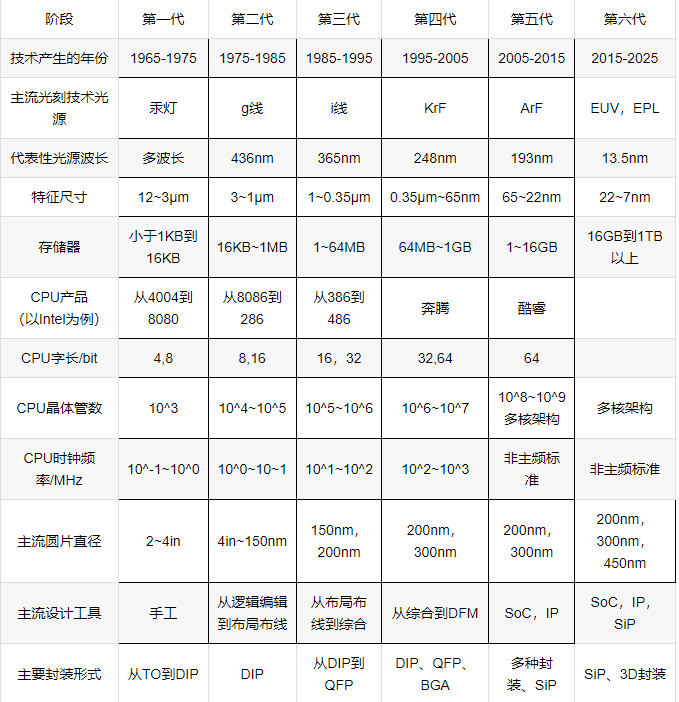

集成电路制造技术发展的重要里程碑二、集成电路产业的发展规律2.1 半导体产品制造技术约10年一代的技术进步 2.2 集成电路从研发到批量生产约需10年的案例典型

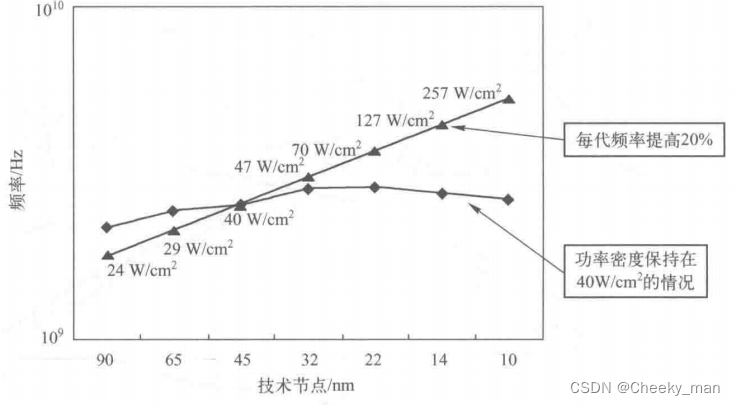

2.2 集成电路从研发到批量生产约需10年的案例典型 2.3 摩尔定律的终结与软件的创新 沿着摩尔预测的集成电路发展路径,集成电路加工线宽逐渐减小,2015年最小线宽已经达到7mm,进入介观物理学的范畴。继续单纯缩小沟道宽度将受到三方面的制约。2.3.1 物理制约介观(Mesoscopic)尺度的材料,一方面,含有一定量粒子,无法仅仅用薛定谔方程求解;另一方面,其粒子数又没有多到可以忽略统计涨落(Statistical Fluctuation)的程度。这就使得集成电路技术的进一步发展遇到很多物理障碍,如费米钉扎(Fermi Pinning)、库伦阻塞(Coulomb Blockade)、量子隧穿(Quantum Tumnelling)、杂质涨落(Impurity Fluctuation)、自旋输运(Spin Transport)等,需用介观物理和基于量子化的处理方法来解决。2.3.2 功耗制约提高器件性能(以时钟频率为代表参数)与降低功耗之间的矛盾如图所示。

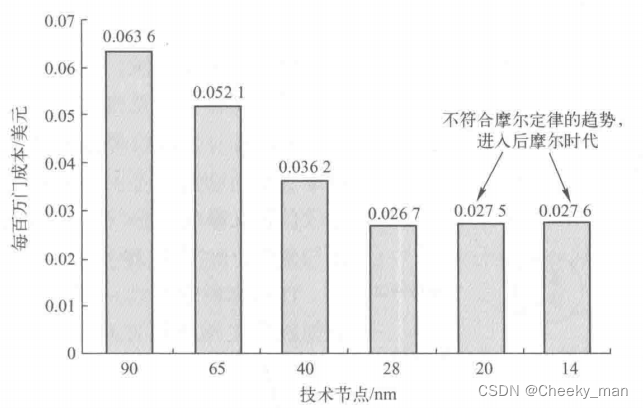

2.3 摩尔定律的终结与软件的创新 沿着摩尔预测的集成电路发展路径,集成电路加工线宽逐渐减小,2015年最小线宽已经达到7mm,进入介观物理学的范畴。继续单纯缩小沟道宽度将受到三方面的制约。2.3.1 物理制约介观(Mesoscopic)尺度的材料,一方面,含有一定量粒子,无法仅仅用薛定谔方程求解;另一方面,其粒子数又没有多到可以忽略统计涨落(Statistical Fluctuation)的程度。这就使得集成电路技术的进一步发展遇到很多物理障碍,如费米钉扎(Fermi Pinning)、库伦阻塞(Coulomb Blockade)、量子隧穿(Quantum Tumnelling)、杂质涨落(Impurity Fluctuation)、自旋输运(Spin Transport)等,需用介观物理和基于量子化的处理方法来解决。2.3.2 功耗制约提高器件性能(以时钟频率为代表参数)与降低功耗之间的矛盾如图所示。 提高时钟频率与降低功耗的矛盾 随着技术节点的推进,器件的时钟频率以20%的幅度提高,但器件的功率密度也大幅度增加。如果将功率密度保持在40W/cm²,则最高时钟频率又无法提高,甚至采用14nm技术节点之后,其时钟频率反而有所下降。2.3.3 经济制约下图表明,90nm 技术节点的每百万门成本为0.0636美元,其后,65nm、40nm至28nm的成本一直呈下降趋势;但是,在进入20nm技术节点后,每百万门的成本将不再按摩尔定律下降,反而有所上升。

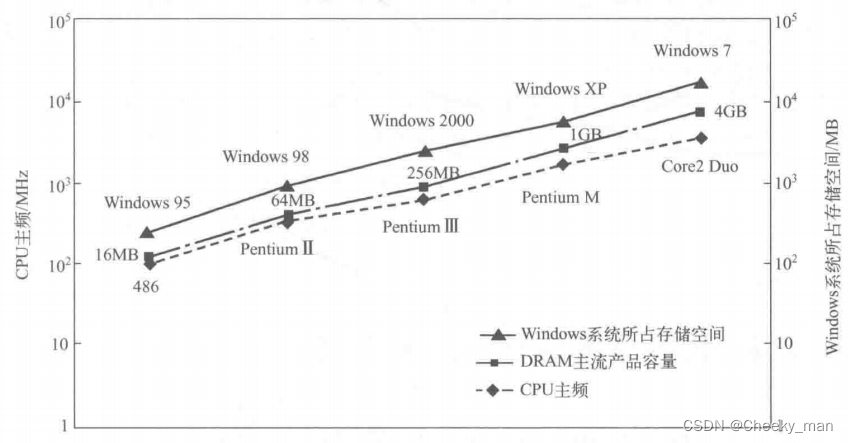

提高时钟频率与降低功耗的矛盾 随着技术节点的推进,器件的时钟频率以20%的幅度提高,但器件的功率密度也大幅度增加。如果将功率密度保持在40W/cm²,则最高时钟频率又无法提高,甚至采用14nm技术节点之后,其时钟频率反而有所下降。2.3.3 经济制约下图表明,90nm 技术节点的每百万门成本为0.0636美元,其后,65nm、40nm至28nm的成本一直呈下降趋势;但是,在进入20nm技术节点后,每百万门的成本将不再按摩尔定律下降,反而有所上升。 也就是说,今后在更高速度、更低功耗和更低成本这三者中,如果以成本作为主要指标,则性能与功耗再难有大的改善;反之,芯片厂商和用户若以性能和功耗为主要诉求,则必须付出相应的代价,而不再享受摩尔定律带来的成本降低的“福利”。但是,如果采用新材料和新器件模型,集成电路集成度是否还能继续沿摩尔定律增长,还有待今后的实践检验。2.3.4 软件协同集成电路对生态体系依赖度增大,需要软硬件协同发展。例如,CPU的竞争绝不仅是CPU芯片本身的竞争,而更多体现在生态系统的竞争。如Intel的CPU与Microsoft的操作系统构建了稳固的Wintel产业发展环境,ARM公司也与Google公司在移动终端领域构建了ARM-Android体系。信息产业最开始是硬件(集成电路)技术驱动,随着集成电路加工技术的进步,单一芯片的集成度越来越高,集成电路的工作速度越来越快,存储器容量越来越大,承载在集成电路上的软件就可以越来越丰富,软件的功能也就越来越强大,应用软件的种类也就越来越多。Windows操作系统所占空间、Intel CPU主频与同期DRAM典型产品存储容量的正相关关系如图所示。

也就是说,今后在更高速度、更低功耗和更低成本这三者中,如果以成本作为主要指标,则性能与功耗再难有大的改善;反之,芯片厂商和用户若以性能和功耗为主要诉求,则必须付出相应的代价,而不再享受摩尔定律带来的成本降低的“福利”。但是,如果采用新材料和新器件模型,集成电路集成度是否还能继续沿摩尔定律增长,还有待今后的实践检验。2.3.4 软件协同集成电路对生态体系依赖度增大,需要软硬件协同发展。例如,CPU的竞争绝不仅是CPU芯片本身的竞争,而更多体现在生态系统的竞争。如Intel的CPU与Microsoft的操作系统构建了稳固的Wintel产业发展环境,ARM公司也与Google公司在移动终端领域构建了ARM-Android体系。信息产业最开始是硬件(集成电路)技术驱动,随着集成电路加工技术的进步,单一芯片的集成度越来越高,集成电路的工作速度越来越快,存储器容量越来越大,承载在集成电路上的软件就可以越来越丰富,软件的功能也就越来越强大,应用软件的种类也就越来越多。Windows操作系统所占空间、Intel CPU主频与同期DRAM典型产品存储容量的正相关关系如图所示。 当前,集成电路的容量和速度已经能够满足几乎任何软件的需要,在这种情况下,信息产业由软件驱动的趋势开始显现,即根据不同操作系统开发适用该软件的硬件。移动通信是最好的例证。目前在市场中占主流的操作系统是安卓和iOS,所有的硬件解决方案要依据这两个操作系统来开发,可以使用不同厂家的但可以运行上述系统的嵌入式CPU、接收与发射芯片、人机界面芯片来制造不同用途、不同功能、不同型号的手机。这就是软件定义系统,系统决定集成电路的设计与生产,如图所示。

当前,集成电路的容量和速度已经能够满足几乎任何软件的需要,在这种情况下,信息产业由软件驱动的趋势开始显现,即根据不同操作系统开发适用该软件的硬件。移动通信是最好的例证。目前在市场中占主流的操作系统是安卓和iOS,所有的硬件解决方案要依据这两个操作系统来开发,可以使用不同厂家的但可以运行上述系统的嵌入式CPU、接收与发射芯片、人机界面芯片来制造不同用途、不同功能、不同型号的手机。这就是软件定义系统,系统决定集成电路的设计与生产,如图所示。 TI首席科学家Gene Frantz认为∶大部分创新是在基于硬件基础上的软件创新。硬件将成为创新设计人员思路拓展平台的一部分。

TI首席科学家Gene Frantz认为∶大部分创新是在基于硬件基础上的软件创新。硬件将成为创新设计人员思路拓展平台的一部分。来源:车规半导体硬件

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。